A test for FPGA behavior written in System Verilog. Involves coverage and test cases.

Example Test Bench Creation

- Create the verilog module:

module andprogram(

input reg a,

input reg b,

output reg c

);

assign c = a & b;

endmodule- Create the test bench:

`timescale 1ns / 1ps

module andtest();

logic [1:0] mySW;

logic myOut;

andprogram module_under_test(mySW[1], mySW[0], myOut);

initial begin

#100 mySW = 2'b00;

#100 mySW = 2'b01;

#100 mySW = 2'b10;

#100 mySW = 2'b11;

end

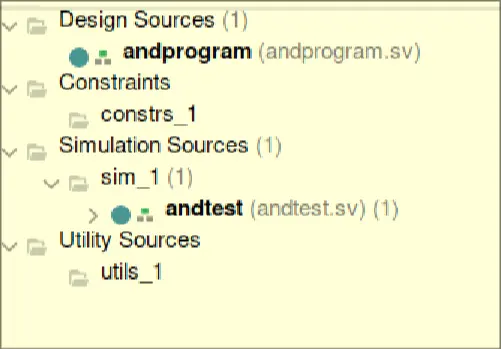

endmodule- Project structure looks like this:

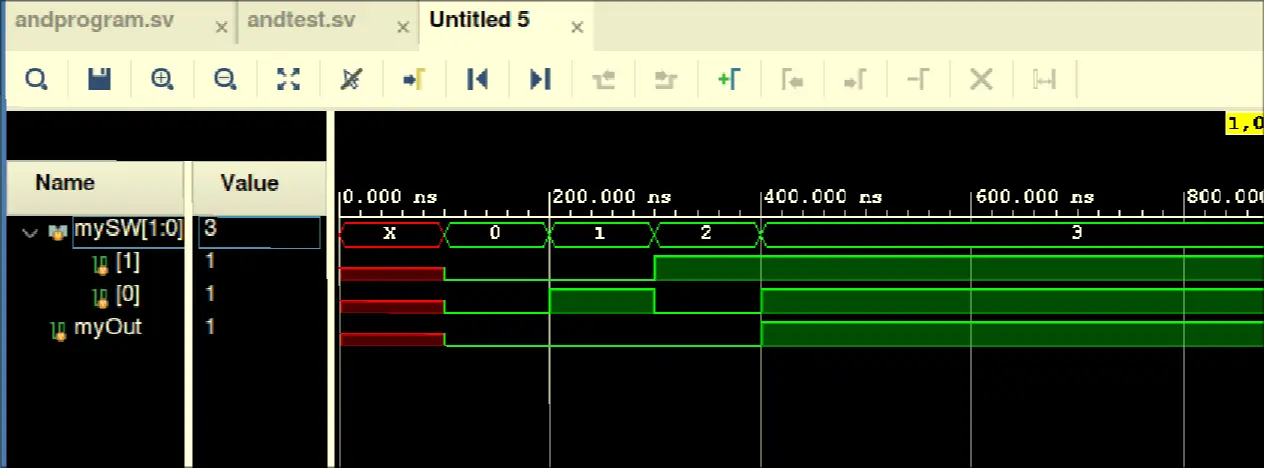

- Run the Vivado Behavioral Simulation simulation looks: